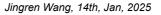

#### Don't care cheatsheet

### **Internal Don't Care**

Don't cares derived from network structure.

### Satisfiability Don't Care(SDC)

SDC is not easy to "draw" on a graph, the main idea is that there are lots of intermediate representation between node N and PIs, but not all minterms are used, so even in a complete specified local function, you could still represent the node N using those minterms not showing up as "don't cares".

# **Observability Don't Care(ODC)**

Generally speaking, f\_N can be represented by  $x_1, x_2, x_3$  independently, without influencing by Node y.

Or, you could say that by assigning value 0/1 to y makes no difference to the result of  $f_N$ .

## External Don't Care(EXDC)

Don't cares from user, not from network structure.

# External Controllability Don't Care(EXCDC)

This is due to the environment/context specification, some of the value X combination of the inputs will never appear.

Note that this is a special case of extending SDC from local inputs to PIS.

# External Observability Don't Care(EXODC)

Case 1: Function of PIs

To some POs, some PIs are not observed.

Note that this is a special case of ODC extending to PIs and POs.

This case is also related to the specification of .exdc in BLIF format.

# External Observability Don't Care(EXODC)

Case 2: Function of other POs

To some POs, some other POs are not observed.

This is based on the actual network implementation, some of the POs have higher priority than others, for example, a cascaded next stage logic, which will have other lower priority POs not observed.

#### Reference

1. Lee, SY., Riener, H., De Micheli, G. (2023). External Don't Cares in Logic Synthesis. In: Drechsler, R., Huhn, S. (eds) Advanced Boolean Techniques. Springer, Cham. https://doi.org/10.1007/978-3-031-28916-3\_3

2. Laung-Terng Wang, Yao-Wen Chang, and Kwang-Ting (Tim) Cheng. 2009. Logic synthesis in a nutshell. Electronic Design Automation: Synthesis, Verification, and Test. Morgan Kaufmann Publishers Inc., San Francisco, CA, USA. 299-404.

3. https://course.ece.cmu.edu/~ee760/760docs/blif.pdf

4. https://cseweb.ucsd.edu/classes/fa23/cse248-a/slides/lec07\_2pJiang.pdf